MIPS R10000

T5, 250.0 MHz

| Specifications | |

|---|---|

| Designer | MIPS |

| Family | R10000 |

| Model | |

| Code Name | T5 |

| Clock [MHz] | 250.0 |

| Max Clock (Turbo) [MHz] | |

| Physical Details | |

|---|---|

| Voltage (Nom.) [V] | 3.30 |

| TDP [W] | |

| Die Size [mm²] | 298 |

| Transistor [M] | 6.8 |

| Architecture | |

|---|---|

| Data Path Width | 64 |

| Cores per Chip | 1 |

| Threads per Core | 1 |

| Microarchitecture | |

|---|---|

| µarch | R10000 |

| ISA | |

| FP Pipe Stages | 7 |

| Int Pipe Stages | 5 |

| Cache (on-chip) | |

|---|---|

| L1 Unified Cache | |

| L1 Instruction Cache | 32 |

| L1 Data Cache | 32 |

| L2 Cache | |

| L3 Cache | |

| Cache (off-chip) | |

|---|---|

| L1 Unified Cache | |

| L1 Instruction Cache | |

| L1 Data Cache | |

| L2 Cache | 1024 |

| L3 Cache | |

| Process Technology | |

|---|---|

| Fabricated By | NEC |

| Process | http://cpudb.stanford.edu/technologies/83 |

| Technology | CMOS |

| Feature Size [μm] | 0.35 |

| Channel Length [μm] | 0.35 |

| Metal Layers | 4 |

| Metal Type | |

| FO4 Delay [ps] | 126.0 |

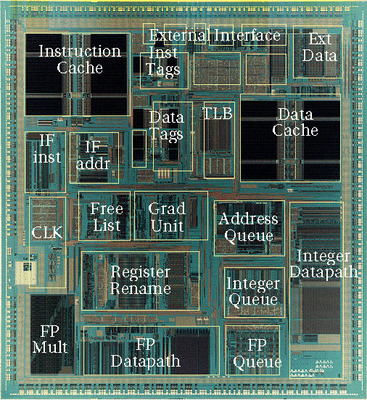

Die Photo

SpecInt1995

| Go | M88ksim | Gcc | Compress | Li | Ijpeg | Perl | Vortex | |

|---|---|---|---|---|---|---|---|---|

| 12.8 | 11.3 | 10.3 | 12.1 | 11.8 | 11.2 | 15.7 | 9.8 | source |

| 13.3 | 11.8 | 12.0 | 13.9 | 11.8 | 12.0 | 16.4 | 13.7 | source |

| 14.3 | 11.8 | 13.0 | 14.9 | 12.2 | 12.3 | 16.7 | 19.6 | source |

| 14.6 | 14.1 | 15.2 | 15.4 | 11.6 | 12.5 | 17.2 | 22.5 | source |

| 13.5 | 13.1 | 13.3 | 15.2 | 12.9 | 12.6 | 14.2 | 12.2 | source |

| 13.7 | 13.3 | 13.9 | 15.5 | 13.1 | 12.9 | 14.3 | 12.6 | source |

| 13.6 | 13.3 | 13.7 | 15.5 | 13.1 | 13.1 | 14.4 | 12.9 | source |