Intel Pentium

P5, 60.0 MHz

| Specifications | |

|---|---|

| Designer | Intel |

| Family | Pentium |

| Model | |

| Code Name | P5 |

| Clock [MHz] | 60.0 |

| Max Clock (Turbo) [MHz] | |

| Physical Details | |

|---|---|

| Voltage (Nom.) [V] | 5.00 |

| TDP [W] | 13.0 |

| Die Size [mm²] | 294 |

| Transistor [M] | 3.2 |

| Architecture | |

|---|---|

| Data Path Width | 32 |

| Cores per Chip | 1 |

| Threads per Core | 1 |

| Microarchitecture | |

|---|---|

| µarch | P5 |

| ISA | x86-32 |

| FP Pipe Stages | 6 |

| Int Pipe Stages | 5 |

| Cache (on-chip) | |

|---|---|

| L1 Unified Cache | |

| L1 Instruction Cache | 8 |

| L1 Data Cache | 8 |

| L2 Cache | |

| L3 Cache | |

| Cache (off-chip) | |

|---|---|

| L1 Unified Cache | |

| L1 Instruction Cache | |

| L1 Data Cache | |

| L2 Cache | 256 |

| L3 Cache | |

| Process Technology | |

|---|---|

| Fabricated By | Intel |

| Process | http://cpudb.stanford.edu/technologies/54 |

| Technology | BICMOS |

| Feature Size [μm] | 0.8 |

| Channel Length [μm] | 0.8 |

| Metal Layers | |

| Metal Type | |

| FO4 Delay [ps] | 288.0 |

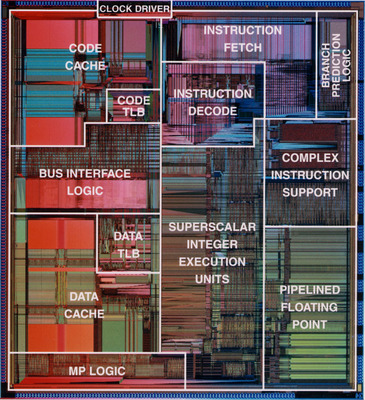

Die Photo

SpecInt1992

| Espresso | Li | Eqntott | Compress | Sc | Gcc | |

|---|---|---|---|---|---|---|

| 51.5 | 74.1 | 66.7 | 36.5 | 164.1 | 44.8 | source |

| 58.4 | 77.7 | 62.5 | 36.0 | 86.5 | 55.0 | source |

| 54.6 | 76.0 | 63.6 | 40.5 | 164.7 | 50.8 | source |

SpecFp1992

| Spice2g6 | Doduc | Mdljdp2 | Wave5 | Tomcatv | Ora | Alvinn | Ear | Mdljsp2 | Swm256 | Su2cor | Hydro2d | Nasa7 | Fpppp | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 40.3 | 47.4 | 55.0 | 33.1 | 59.0 | 58.1 | 102.8 | 111.2 | 27.3 | 28.1 | 31.5 | 52.5 | 35.2 | 60.9 | source |