IBM PowerPC 604

120.0 MHz

| Specifications | |

|---|---|

| Designer | IBM |

| Family | PowerPC 604 |

| Model | |

| Code Name | |

| Clock [MHz] | 120.0 |

| Max Clock (Turbo) [MHz] | |

| Physical Details | |

|---|---|

| Voltage (Nom.) [V] | 2.50 |

| TDP [W] | |

| Die Size [mm²] | 196 |

| Transistor [M] | 3.6 |

| Architecture | |

|---|---|

| Data Path Width | 32 |

| Cores per Chip | 1 |

| Threads per Core | 1 |

| Microarchitecture | |

|---|---|

| µarch | PowerPC 604 |

| ISA | |

| FP Pipe Stages | 8 |

| Int Pipe Stages | 6 |

| Cache (on-chip) | |

|---|---|

| L1 Unified Cache | |

| L1 Instruction Cache | 16 |

| L1 Data Cache | 16 |

| L2 Cache | |

| L3 Cache | |

| Cache (off-chip) | |

|---|---|

| L1 Unified Cache | |

| L1 Instruction Cache | |

| L1 Data Cache | |

| L2 Cache | 512 |

| L3 Cache | |

| Process Technology | |

|---|---|

| Fabricated By | IBM |

| Process | http://cpudb.stanford.edu/technologies/40 |

| Technology | CMOS |

| Feature Size [μm] | 0.35 |

| Channel Length [μm] | 0.35 |

| Metal Layers | 4 |

| Metal Type | |

| FO4 Delay [ps] | 126.0 |

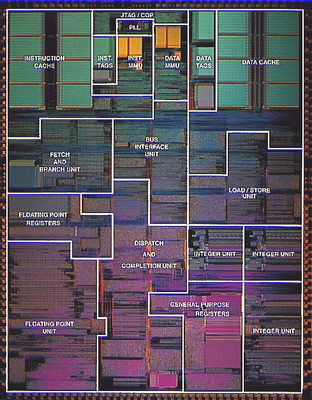

Die Photo

SpecInt1992

| Espresso | Li | Eqntott | Compress | Sc | Gcc | |

|---|---|---|---|---|---|---|

| 138.4 | 121.5 | 164.2 | 72.9 | 226.5 | 92.4 | source |

| 133.5 | 115.9 | 157.1 | 73.5 | 213.7 | 86.5 | source |

| 133.5 | 114.8 | 161.8 | 77.4 | 216.7 | 88.2 | source |

| 108.6 | 96.7 | 126.4 | 53.6 | 169.7 | 61.5 | source |

SpecFp1992

| Spice2g6 | Doduc | Mdljdp2 | Wave5 | Tomcatv | Ora | Alvinn | Ear | Mdljsp2 | Swm256 | Su2cor | Hydro2d | Nasa7 | Fpppp | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 77.4 | 155.0 | 216.8 | 103.6 | 73.8 | 176.2 | 206.7 | 369.0 | 122.3 | 51.6 | 102.1 | 110.4 | 79.7 | 231.2 | source |

| 72.8 | 142.0 | 214.2 | 104.5 | 108.2 | 175.8 | 235.9 | 362.2 | 120.5 | 69.7 | 91.9 | 126.5 | 101.7 | 153.6 | source |

| 81.5 | 143.1 | 211.0 | 104.8 | 95.3 | 174.6 | 248.9 | 368.0 | 121.4 | 72.1 | 94.6 | 135.1 | 108.8 | 155.4 | source |

| 50.8 | 118.5 | 188.1 | 80.1 | 70.3 | 175.4 | 182.7 | 360.7 | 112.4 | 68.2 | 58.3 | 90.7 | 77.5 | 93.2 | source |

SpecInt1995

| Go | M88ksim | Gcc | Compress | Li | Ijpeg | Perl | Vortex | |

|---|---|---|---|---|---|---|---|---|

| 5.0 | 3.9 | 3.9 | 3.7 | 3.5 | 5.4 | 3.3 | 3.8 | source |

| 4.2 | 3.3 | 3.3 | 3.3 | 3.0 | 4.6 | 2.7 | 3.1 | source |

| 4.5 | 4.0 | 3.5 | 3.7 | 3.5 | 5.2 | 3.4 | 3.4 | source |